Now we have to add 9’s complement of B to A.

We want to find out A- B by 9's complement subtraction method.įirst we have to find out 9’s complement of B. We will understand this method of subtraction via an example. Or if we want to find out the 1.Īn example is given below to illustrate the concept of obtaining 1.

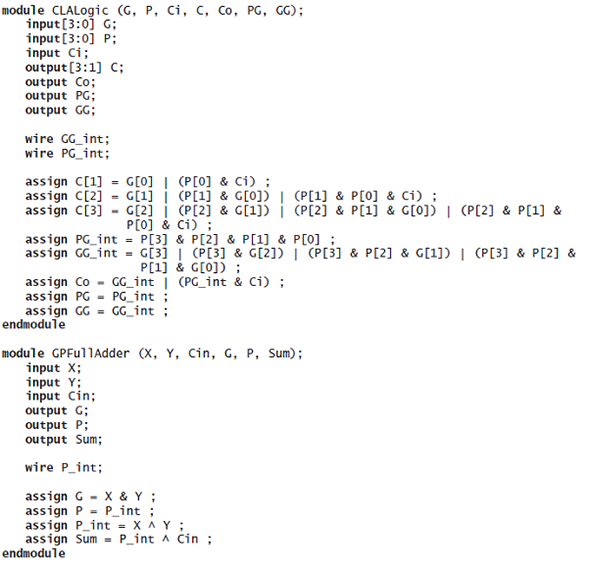

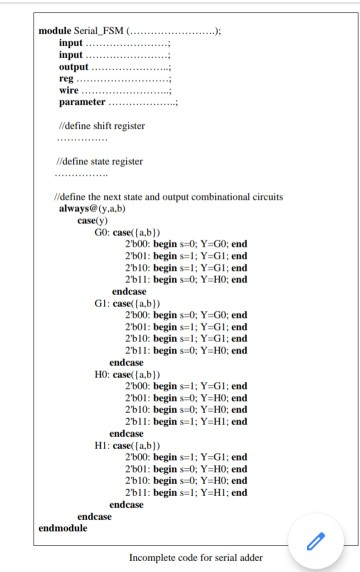

We have to add 1 with the 9's complement of any number to obtain the desired 1. 0's complement, it is relatively easy to find out the 1. VHDL Tutorial: Learn by Example- by Weijun Zhang, July 2001 *** NEW (2010): See the new book VHDL for Digital Design, F. An introduction to delta sigma converters without much theory and mathematics. Using serial port UART transmission module written in verilog, sending rate to 115200, input clock for 50m for many years validation without. ASIC proven Design done FPGA proven Specification done OpenCores Certified. The table given below will explain the 9's complement more easily. To obtain the 9's complement of any number we have to subtract the number with (1. Now first of all let us know what 9's complement is and how it is done.įinal Exam: May 8, 8-10am Project 3 is due on May 8 CS 354 - Digital Systems Design Spring-2017 Classes: MW 9:25am - 10:40am, Maria Sanford Hall 210. In this article we will discuss about the following topics. The complements are used to make the arithmetic operations in digital system easier. A demultiplexer function exactly in the reverse of a multiplexer, that is a demultiplexer. A multiplexer is a circuit that accept many input but give only one output. > Draw the circuit diagram and label the circuit properly.Any warning that comes up when you try to run our applets should emphasize that our applets will always run with “limited access”, which is Oracle’s way of letting you know that teahlab doesn’t do anything on your computer except running the circuits you see: in other words, our applets are safe to run. You will need to think about the "carrys Briefly describe the major design steps and draw a block diagram and the FSM Write down the state transition table. The required design for the serial subtractor can be obtained by modifying the design of the serial adder. all zeros, and the first "1" remain Hint: See the example design of a serial adder in Section 6.5 in the text book. The remaining bits are complimented or inverted. One method would be to implement the "rule" where starting from the LSB (the 1st bit in the serial adder) they are.

To get a negative, the 2's compliment is required. Hint: A subtraction is just an addition of the minuend with the negative of the subtrahend. The numbers are represented in 2's complement form. The subtractor subtracts an n-bit binary number B from an n-bit binary number A. (A Mealy-type FSM has an output dependent upon both the FSM state and its inputs). Transcribed image text: Design a serial subtractor circuit based on a Mealy-type FSM.

0 kommentar(er)

0 kommentar(er)